|

| |

Interconnecting 5v and 3.3v logic

Direct connection

5v to 3.3v

A logic input may be described as "5v tolerant" meaning that even

when powered by a lower supply voltage the device will not be harmed by driving

its input to 5v. In that case a 5v output may be connected to a 3.3v input.

3.3v to 5v

A logic input may be described as "TTL compatible", meaning that it

has a lowered input threshold, typically 2.0v. This means that a 3.3v powered

CMOS device can reliably drive the 5v input high. In that case a 3.3v output may

be connected to a 5v input.

3.3v to a 5v rated LCD module

This special case comes up again and again, due to the abundance of cheap 5v

alphanumeric LCD modules. There are two fairly easy options

1: Operate the LCD from 5v, and rely on the display recognising 3.3v as logic

high. The HD44780U and ST7046 both give a VIH of 2.2V so this is acceptable. This is best reserved for

"write-only" designs as reading the LCD would put 5v on some of the

data pins, though on LPC microcontrollers the pins are 5v tolerant anyway.

2: Operate the LCD from 3.3v and supply a negative contrast voltage. Use your

favourite charge-pump circuit or "nick" the bias from a RS232 driver as

the current is tiny. Add a series pot if needed and that should give sufficient

contrast. You could even configure a microcontroller PWM output to supply the

"pump" waveform. Below-zero voltages for contrast ARE allowed, and

some display types require a negative bias anyway even for 5v operation. 3.3v

operation of a 5v LCD will slow down the internal clock by roughly 25% so

software delay times may need lengthening.

Interconnected tri-state outputs

My advice is to translate to a common logic level before combining outputs on

a bus.

- Warning: Tri-state outputs are frequently NOT over-voltage tolerant. The

upper FET typically has a parasitic diode that will become forward-biased if

the output is driven higher than the supply. Some devices avoid this problem

by isolating the substrate of the upper output FET when in tri-state.

- Even if devices are tolerant beware of contention between a 3.3v and 5v

device outputting simultaneously.

- One place this can be an issue is a SPI bus with multiple devices on

different voltages. An alternative strategy might be to add pull-up

resistors then combine the outputs with a logic AND gate instead of

interconnecting them. This works because the idle output is pulled up to

"1" so the active output passes straight through the gate.

- Before I knew better I once designed a circuit with a tri-state buffer with

a diode in series with its positive supply to prevent backflow. This

actually worked surprisingly well, but meant that the buffer was powered from a supply about

0.6v too low.

Buffered connection (Parts suitable for plug-block, DIP or equivalent)

Note: I'm assuming one of the motivations for using MBED is plug-block

development, and that a list of SMT-only devices would not be very helpful.

Multiple lines, 3.3v to 5v, Available in DIP

For this I would recomend any "74HCT" series part, powered by the

destination supply (5v).

Multiple lines, 5v to 3.3v, Available in DIP

- For this I would consider the 74HC4050 (or 74HC4049) which are notable for

having voltage-tolerant inputs, powered by the destination supply (3.3v).

- The 74AHC... series have voltage-tolerant inputs and Texas Instruments

parts should be available in DIP packages.

Buffered connection (Adapted to DIP)

Buffered connection (Surface mount)

Single lines

For single lines I would advise looking at SOT23-5 or SOT323-5 style

"Tiny" logic, powered by the destination supply.

- MC74VHC1GT125 This part looks very useful as a level translation bridge.

The supply range is 3.0v to 5.5v meaning the output can be made compatible

with either supply voltage, and the input is both 5v tolerant and "TTL

compatible" e.g. it will accept 3.3v logic levels. Remember that

"equivalents" do not always have the same voltage tolerance, some

parts are limited to 3.3v maximum or have an input protection diode that

conducts if the input exceeds the supply.

Multiple lines, mixed function

- SN74LVCC3245A 8 translators, with a direction pin and a tri-state enable pin. Note

that side B is always the 5v side.

- TXB0108PWR is bidirectional and auto-sensing for lines WITHOUT pull-up

resistors, note it tends to pull a logic line to whatever its current state

is, so it will prevent a line from "floating" when it is not

actively driven. Not recommended for I2C, but it is a good candidate for SPI

systems as it will handle the single-data-line bidirectional variant. A

module is available from Adafruit with 0.1" pitch pads. Relatively

expensive.

- TXS0108EPWR is bidirectional and auto-sensing for logic lines that have

pull-up resistors. As it is auto-sensing the signal directions may be mixed.

It should support I2C. Its a relatively expensive option though, and may

lead to raised power consumption if used for logic signals that idle low. I

have not seen a module available with this device, however the TXB and TXS

devices appear to have a common pin-out so it might be possible to change

the chip on the Adafruit module.

- With both the TXB and TXS parts the A side is the lower voltage side and

has the OE pin so the A side typically connects to a microcontroller, also

the B side appears to have better ESD protection.

Problems with incorrect level translation

Be aware that a design that works in prototype may prove unreliable in

production.

- At low speed or DC conditions a typical 5v HCMOS gate will transition at

very near 2.5v, and a 3.3v device will output almost 3.3v, allowing the 3.3v

circuit to drive 5v CMOS parts marginally so an undemanding sub 1MHz

application would be expected to work.

- At raised speeds the HCMOS gate may need an input of 4v (80% of Vdd) in

order to meet its performance specification and the 3.3v device may only

reliably output 3.0v (limited by risetime). At best this will lead to

significant pulse-shortening or stretching, at worst signals may not get

through at all.

- At speeds above 10MHz a 5v CMOS signal driving a 3.3v-compliant input may

lead to noticeable pulse stretching, even though the input requirements have

been met.

- When a production design depends on a logic device's specific voltage

tolerance characteristics it is important to remember that generic devices

with the same function code may not have the same characteristics, meaning

that common substitutions may cause problems. As an example looking at

single buffers in SOT23 package all I checked had over-voltage tolerant

inputs but only some had tolerant outputs.

5v to 3.3v issues

- Raised power consumption if current flows from the 5v section to the 3.3v

section. Note that although this leakage would be expected to source current

to the 3.3v section it is possible that parasitic-transistor effects may

cause current drain from the 3.3v supply as well. This may also lead to noticeable

heating of the device.

- Abnormal operation due to 3.3v section being pulled up to a higher

voltage. This may cause the 3.3v section to output a higher than normal

logic level, potentially hiding other problems.

- Abnormal operation of analogue functions due to current flowing into pin.

This may manifest itself as huge errors in ADC readings, for relatively low

currents. NOTE I do not know if the MBED shows this, it probably doesn't due

to the pin voltage tolerance. The effect was quite noticeable on some other

microcontrollers.

- Latch up damage. This is the bogeyman of mixed voltage circuits, and

thankfully modern logic is very resistant. Latch-up occurs because a CMOS

device contains a PNPN structure as a side effect of its construction, and

this behaves like a very hard to trigger thyristor. A device in latch-up will

present a near short circuit across its supply rails, and may be destroyed

if current is insufficiently limited. If current is limited the device will

recover once the supply voltage collapses, meaning that a serious latch-up

event may be mistaken for a software crash. Fortunately modern parts may

require hundreds of mA before latch-up is a real threat, so even as little as

a 10 ohms series resistance may provide adequate protection.

3.3v to 5v issues

This is generally the safer case, since the reduced voltage is unlikely to

cause damage.

- Raised power consumption may occur due to input not being driven properly

high and causing CMOS cross-conduction.

- Ambiguous logic levels lead to slow low-to-high transitions, this can make

a clock waveform very asymmetric.

- Ambiguous logic levels may fail to register as logic high in extreme

cases.

Separate supplies, same voltage

This is a special case of level translation, where two supplies have the same

voltage but are different in some way. An example would be digital and analogue supplies sourced from different regulators, or just a module-to-module

interconnection. Translation is not required but problems may occur if the

supplies come up at different times, or if one suffers a short circuit. The

CD4050 and 74HC4050 parts should be considered. As a bare minimum current should

be limited by series resistors or by using known "weak" outputs.

Translating other voltages: 12v logic (4000 series CMOS)

It should be possible to translate SPI to 12v and use a 12v shift register to

obtain a large number of 12v "ports". This may be a viable alternative

to a 3.3v register and 8 or more parallel translators.

12v to low level

- 74HC4050 has 15v tolerant inputs

- CD4007UBE can be used to make two downward level shifters (among other

things). Unusually for CMOS it brings the source terminals of the FETs out

on individual pins so it is possible to construct a gate with a lower output

range than its supply rails. It is also notable in that on 4 of the 6 FETs

the source terminals are separated from the substrate.

low level to 12v

- CD4504 has a 5v to 15v translation function and the inputs may be put into

"TTL mode" to enable compatibility with 3.3v logic.

- ULN2803 octal open collector driver

- MIC5821 has eight outputs but has a shift register and several MIC5821

devices may be daisy-chained and controlled by one SPI port. Watch the clock

speed though.

low level to 12 volt BIDIRECTIONAL

A N-type MOSFET could be used in "common gate" mode with the gate

connected to the logic supply or slightly more positive, the source connected to

the low-level logic and the drain connected to the 12 volt circuit. Pull-up

resistors will probably be needed on both sides. If the drain is pulled to

ground externally then the source will be pulled down initially by the body

diode and then by drain to source conduction due to the gate voltage biasing it

on. If the source is driven to ground then the FET will conduct normally.

Other voltages: Bipolar

Bipolar supplies may be usefull to allow a positive-only ADC or DAC to be

used with balanced supplies such as +/- 2.5v. It is also sometimes desirable to

operate 24v relays from a system's +/-12v rails to minimise current, though this

approach originated in systems with symetrical linear supplies e.g. +/-12V, and

is unsuited to modern switching power supplies that have a far greater current

available from the positive supply compared to the negative.

- 74HC4053 analog switch has a Vee pin which accepts a negative supply below

the logic "ground" level though watch out for the 10V limit

- RS232 line driver e.g. MC1488

- RS232 line reciever e.g. MC1489 (Note that the recommended supply is 5v)

- I have seen quad comparators used as relay drivers. One input was biased

to the logic threshold and the device ground was connected to -12v. 24V

relays were used

Special cases

I2C bus level translation

- MANY hardware implementations should be 5v-tolerant, but...

- Frequently a microcontroller implementation may be restricted to 3.3v,

particularly if the I2C pins are multi-function and not dedicated.

- Good results have been obtained with the two-FET translator method in 3.3v

systems (with lower voltages its harder to find a compatible FET), however

please be aware that this method does NOT change the logic threshold of the

low-voltage part (because the FET turns on for logic-low, bypassing it) nor

does it buffer or regenerate the signal.

- Unfortunately for plug-block experimenters most IC solutions appear to be

in very small SMT forms not DIP

- Some I2C translator ICs are really just implementations of the two FET

method, though they may add active pull-up drive to increase speed.

- True I2C buffers exist, these will improve noise immunity and signal

range. Pay attention to datasheets though, because of the bidirectional

nature of I2C these devices may use various "tricks" to determine

signal direction, for example on the microcontroller side the buffer may

only pull down to a specific voltage not ground. The voltage will be low

enough to register as a logic low on the micro, but not low enough to

activate the buffer's line driver.

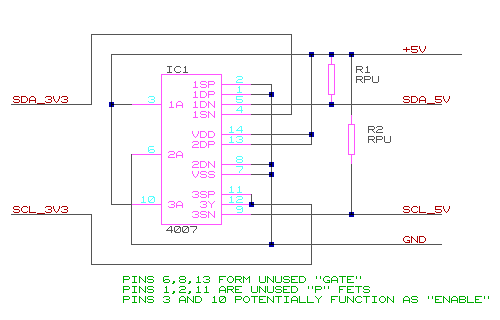

- For those looking for an all DIP IC solution, for example for plugblock

or stripboard designs, it may be worth looking at the CD4007UBE instead

of discrete pass transistors. Biased from 5V the N-channel FETs would only

pull up to 2V on the part I tried, but would pull down sufficiently to work

with a 4.7k pull-up. As these are effectively 4-terminal FETS if the gate

was taken to 0v the device would isolate completely. Drawbacks would be a

relatively high on-resistance and a complete dependence on passive pull-up.

A "Plugblock compatible" I2C translator. Due to the FETs having

grounded substrate it doesn't matter which side is the higher voltage side, and

with no parasitic diode it can be disabled to isolate the busses.

|